Page 1 of 1

Reverse Engineering a Sound Board...

Posted: Sat Aug 05, 2017 10:05 pm

by 1024MAK

I'm just reverse engineering a sound board...

Here's a schematic:

Who wants to have a go at explaining the address decoding and operation

Then I will compare your thoughts to my thoughts (not had a chance to test it yet, as some repairs are needed to it...)

Mark

Re: Reverse Engineering a Sound Board...

Posted: Sat Aug 05, 2017 10:38 pm

by Andy Rea

okie quick look not really worked anything out.... spent more time finding out what that was hanging off the ay chip... prom uh... interesting way of adding some fixed information, set address on one of the eight bit ports, read the data in the other port...

so decoding... interesting there is no /rd or /wr but a /m1 and /iorq ... M1 must be high along with bits 0-5 on the address bus and iorq low

then looks like bit 6 is determining whether it is a read or write

and bit 7 is selecting write register select or write/read register

it looks interesting to say the least..

regards Andy

Re: Reverse Engineering a Sound Board...

Posted: Sat Aug 05, 2017 11:21 pm

by 1024MAK

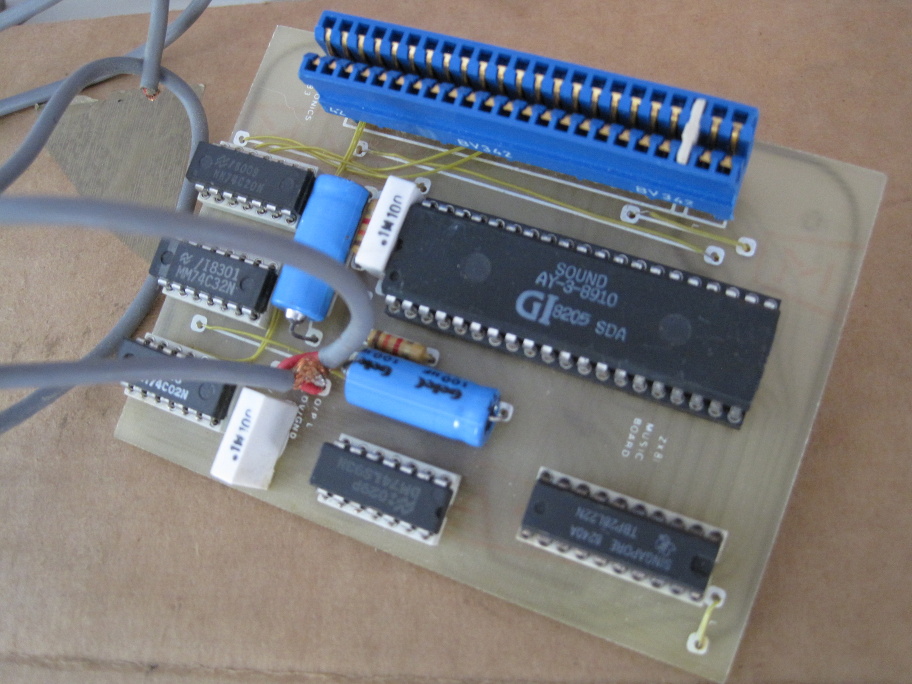

Photo:

- Photo of ZX81 Sound Board

- ZX81 Sound Board scaled25.JPG (221.22 KiB) Viewed 1900 times

Mark

Re: Reverse Engineering a Sound Board...

Posted: Sun Aug 06, 2017 4:23 pm

by sirmorris

1024MAK wrote: ↑Sat Aug 05, 2017 10:05 pmWho wants to have a go at explaining the address decoding and operation

Me! Me! At least the AY side of things.

The AY has 3 control pins, it's not a chip-select scheme to speak of. One of the control pins can be tied high without affecting the logic. In my case I tied BC2 high. And in this case too I see.

Here's the selection code from the ZXpand+ CPLD.

Code: Select all

// AY IO

assign AYIO1 = A[7:0] == 8'hcf | A[7:0] == 8'hdf;

assign AYIO2 = A[7:0] == 8'h0f | A[7:0] == 8'h1f;

// bdir bc1 mode

// 0 0 inactive

// 0 1 read

// 1 0 write

// 1 1 address

assign BDIR = (AYIO1 | AYIO2) & nM1 & !nIORQ & nRD;

assign BC1 = AYIO1 & nM1 & !nIORQ;

So when either of the AY's ports are accessed for a write BDIR is 1.

When the address port is accessed BC1 is 1.

M1 is typically factored into the logic because M1 and IORQ asserted at the same time is an interrupt ack, not an IO request.

HTH